VT vs. FIN

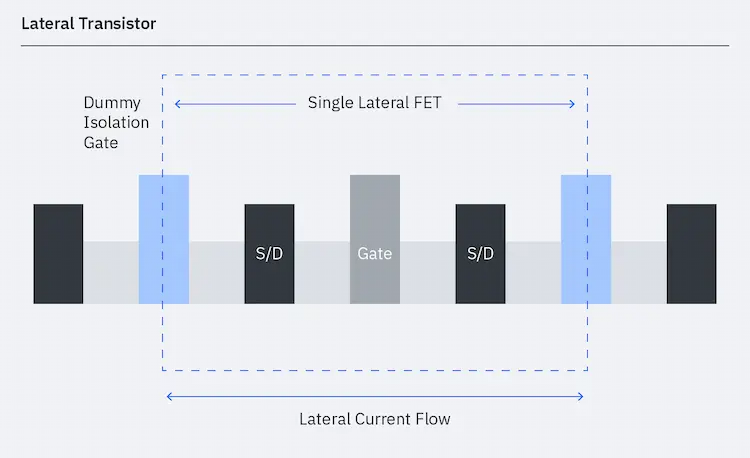

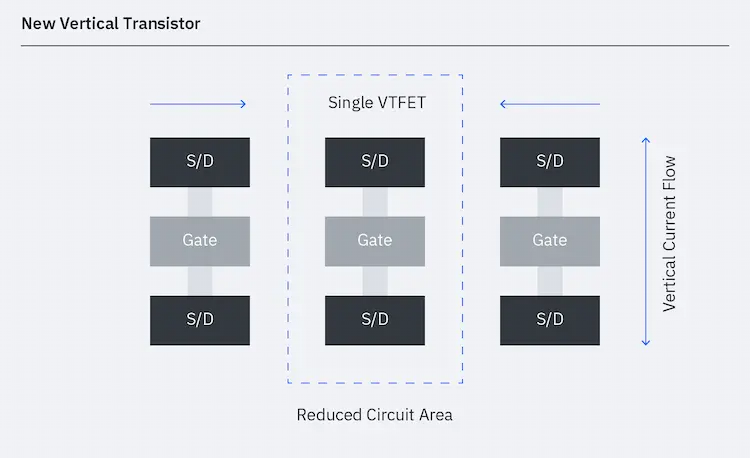

Samsung and IBM have found a way to stack source, drain, and gate structures in order to further increase the number of transistor cells on a wafer. According to both companies, the technology will allow for two times the performance of current FinFET technology and up to an 85% power savings without reducing the space (pitch) between each transistor, which also reduces the distance power has to travel and the distance between vertical cells, which improves performance, along with the ability to be less constrained as to the size of each sorce, drain, and gate structure.

All in, this is a step toward another iteration in the ability to produce circuitry that is required for faster and more complex computing, without the issues facing sub-nanometer node production. Neither company has set a timetable for products using the technology, but we would expect early versions to be shown next year, although real implementation will likely take a few years to further define production processes. It is certainly a step forward in IC design.

RSS Feed

RSS Feed