Getting Smaller

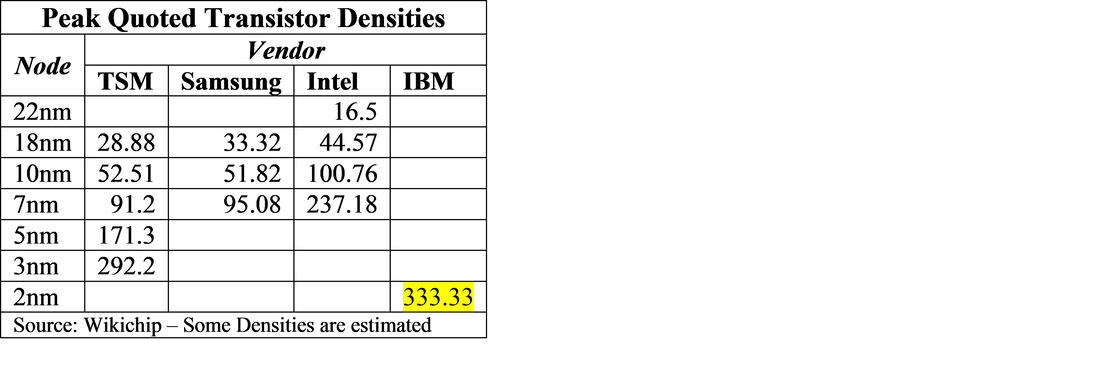

That said, the transistor density is till the measurement point for process nodes, and while they vary from manufacturer t manufacturer and fab to fab, the table below gives an idea of the density of transistors from various manufacturers at each process node, shown as ‘millions of transistors/mm2, and how they can differ. IBM is using a 3 stack configuration to achieve higher densities (assumed) while Samsung will introduce a 3 stack cell at the 3nm node, while TSM is expected to wait until the 2nm node. While IBM uses Samsung’s foundry services for much of its actual chip production, it is likely a jump ball as to who will be first to use the technology, which based on the estimates, would see a performance increase of 45% and an energy consumption reduction of 75% relative to the 7nm process.

RSS Feed

RSS Feed